# Keysight Technologies

M8190A Arbitrary Waveform Generator

12 GSa/s Arbitrary Waveform Generator

Data Sheet

# High resolution + wide bandwidth in an AWG

## M8190A Arbitrary Waveform Generator (AWG)

## M8190A at a glance

- Precision AWG with two DAC settings

- 14-bit resolution up to 8 GSa/s

- 12-bit resolution up to 12 GSa/s

- Variable sample rate from 125 MSa/s to 8/12 GSa/s

- Spurious-free-dynamic range (SFDR) up to 90 dBc typical

- Harmonic distortion (HD) up to -72 dBc typical

- Up to 12.25 effective number of bits (ENOB)

- Up to 2 GSa arbitrary waveform memory per channel with advanced sequencing

- Analog bandwidth 5 GHz

- Optional real-time digital signal processing in Keysight Technologies, Inc. proprietary ASIC for:

- Digital up-conversion to IF

- Changing waveform parameters on the fly

- Form-factor: 2 U AXIe module, controlled via external PC or AXIe system controller

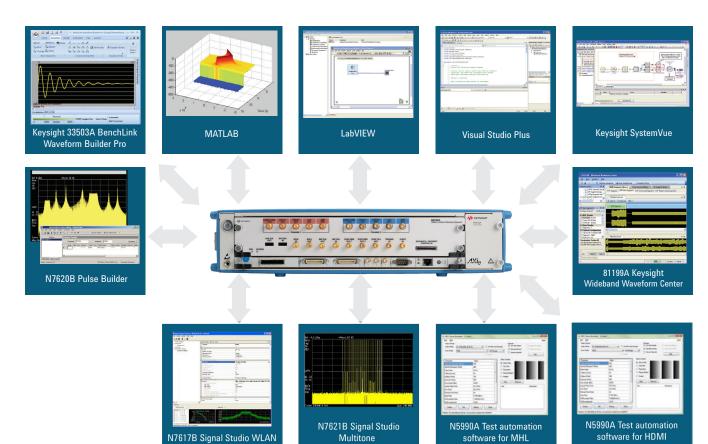

- Supported software: Keysight Benchlink Waveform Editor, MATLAB, LABVIEW, Keysight Signal Studio Pulsebuilder, Signal Studio WLAN, Test automation software support for MHL and HDMI; planned support for Signal Studio Multitone

#### Waveform file import capability

- Import waveform format by series:

- TXT file format (Compatibility: Keysight M8190A)

- TXT14 file format (Compatibility: Keysight M8190A)

- BIN file format (Compatibility: Keysight M8190A.

Recommended as standard binary file import format.)

- IQBIN file format (Compatibility: Keysight M8190A.

Recommended as standard binary file import format.)

- BIN6030 file format (Compatibility: Keysight N6030A Arbitrary Waveform Generator, 15-Bit, 1.25 GS/s)

- BIN5110 file format (Compatibility: Keysight 5110A)

- N5110B Baseband Studio for Waveform Capture -Keysight

- N5110A Baseband Studio for Waveform Streaming

- LiCensed (SigStudioEncrypted in the SFP) file format (Compatibility: Keysight Signal Studio generated encrypted file)

- MAT89600 (Compatibility: 89600 VSA)

- DSA90000 (Compatibility: DSA90000 Oscilloscope)

- CSV (Compatibility: Keysight M8190A)

## Three amplifiers for different applications

- Direct DAC optimized for best SFDR & HD

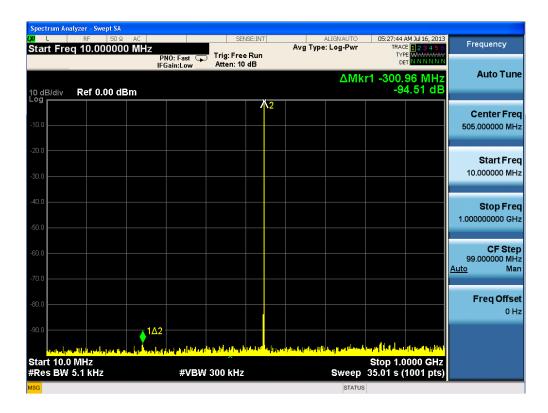

- SFDR up to -90 dBc (typ), fout = 100 MHz, measured DC to 1 GHz

- Amplitude ~350 mVpp ... 700 mVpp, offset -20 mV ...

+20 mV

- Differential output

- DC amplifier¹ optimized for serial data/time domain applications

- Amplitude 500 mVpp ... 1.0 Vpp; (overprogramming down to 150 mV possible) output voltage window: –1.0 V ... +3.3 V

- t<sub>rise/fall, 20% 80%</sub> < 60 ps

- Differential output

- AC amplifier<sup>1</sup> optimized to generate high voltage, high bandwidth signals

- 50 MHz to 5 GHz bandwidth

- Single ended, AC coupled output

- Amplitude: 200 mVpp ... 2.0 Vpp

#### M8192A Multi-Channel Synchronization Module

- Phase coherent synchronization of up to 6 M8190A modules (= 12 channels)

- One trigger input can trigger up to 6 M8190A modules with deterministic latency

- Skew repeatability of 2 ps between any two channels independent of sample rate

- Skew calibration with 50 fs delay resolution between any two channels

- 1U AXIe module for high port density

- 1. AMP option

## **Enhance Your Reality**

A better name for an advanced arbitrary waveform generator is a "signal scenario generator" or SSG.

This description signifies a level of versatility that enables you to set up complex real-world signals—whether you need precise signals to characterize the performance of a design or need to stress a device to its limits. From low-observable radar to high-density communications, testing is more realistic with precision arbitrary waveform generation from an SSG.

Take reality to the extreme: A Keysight AWG is the source of greater fidelity, delivering high resolution and wide bandwidth—simultaneously. This unique combination lets you create signal scenarios that push your designs to the limit and bring new insights to your analysis. Get bits and bandwidth—and enhance your reality.

High-quality signal generation is the foundation of reliable and repeatable measurements. The Keysight M8190A ensures accuracy and repeatability with 14-bit resolution, up to 8 GSa/s sampling rate and up to 90 dBc SFDR. High dynamic range and excellent vertical resolution gives you confidence that you are testing your device, not the signal source.

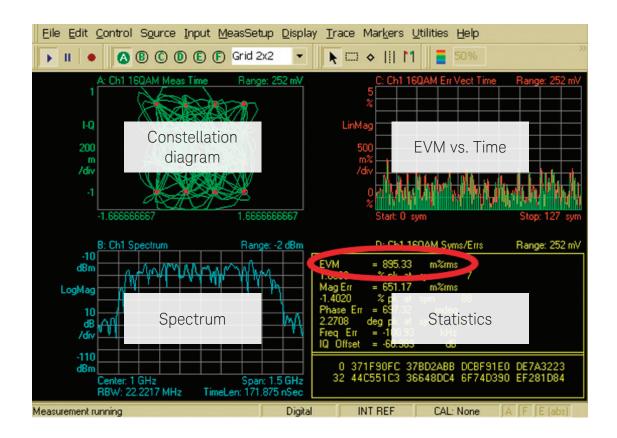

As an example, a test setup that exhibits a high error vector magnitude (EVM) reading might prevent you from seeing problems within your device under test (DUT). The level of reality possible with the M8190A minimizes problems like this.

Get reliable, repeatable measurements from precise signal simulations

#### Versatile

## Optimize the output to match your application

An AWG is the most versatile signal scenario generator possible. Capabilities such as easy switching between 14-bit output at 8 GSa/s and 12-bit output at 12 GSa/s help you handle multiple applications and measurement requirements.

Because every application calls for different signal characteristics, the Keysight M8190A also contains three amplifiers that are optimized for I/Q signals, IF/RF output, or clean time-domain signals. You can switch between them as needed through software commands. Some applications call for Multi-channel support. The M8192 AXIe module can be plugged into the chassis ensuring alignment up to 12-channels.

# Optimized for different signal characteristics

Best SFDR and HD

- Single-ended or differential output

- Amplitude 350 mV $_{pp}$  ... 700 mV $_{pp}$ , single-ended

- Offset -20 mV ... +20 mV

- Direct output

- Adjustable differential offset

High bandwidth high voltage

- Up to 5 GHz

- Single-ended, AC coupled output

- Amplitude 200 mV<sub>pp</sub> to 2.0 V<sub>pp</sub>, single-ended

- AC amplifier 1

Time domain measurements low jitter

- Single-ended or differential,

DC-coupled output

- Amplitude 500 mV  $_{\rm pp}$  ... 1.0 V  $_{\rm pp}$  single-ended

- Output voltage window

- -1.0 V to +3.3 V

- Transition times (20/80)60 ps

- DC amplifier 1

1. AMP option

Create complex signal scenarios—efficiently

## Memory

Highly realistic testing often requires long play times and long signal scenarios

For example, 2 GSa of memory combined with advanced sequencing capabilities allow you to use the memory efficiently and effectively.

Direct access to individual memory segments is possible in real time through the dynamic sequence control input. You can create waveforms and download them into the M8190A using software applications such as Signal Studio Pulse Builder, Multi-tone and WLAN; SystemVue, MATLAB, LabView or your own routines written in C++, C# or Visual Basic.

For sensitive applications, memory storage is not persistent: Memory contents are volatile and are erased when power is turned off.

## Configure

# Assemble the best configuration for your application

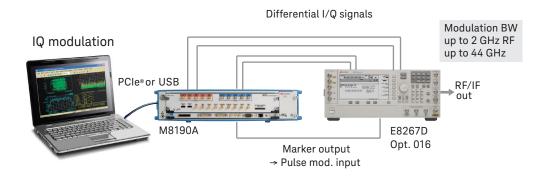

The typical test setup shown to the right covers high RF applications up to 40 or 60 GHz. In this case the M8190A generates differential I/Q signals that are sent to an upconverter such as the Keysight PSG signal generator. The M8190A is packaged in the AXIe form factor, which reduces system size, weight and footprint.

The block diagrams shown to the right illustrate configurations for I/Q modulation and direct IF/RF output. The M8190A supports direct generation of IF signals: Because this is done digitally, signal quality is outstanding. The instrument provides an analog bandwidth of 5 GHz; if higher output frequency is needed a mixer must be added to the configuration.

## Multi-level signals

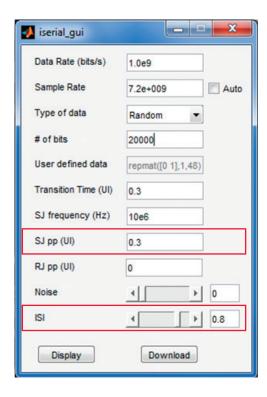

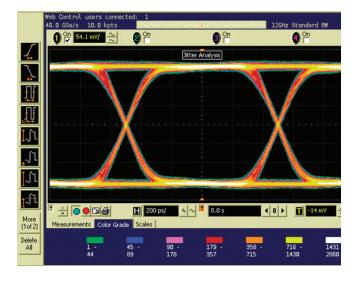

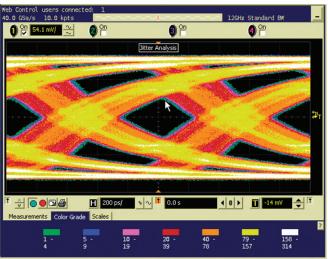

Jitter and noise cause misalignment of edges and levels, resulting in data errors.

The M8190A is equipped to ensure flexible modifications to fit new distortion requirements by simply adapting the waveform itself. You can easily mimic analog imperfections that occur in real-world environments by using mathematical description in tools such as MATLAB. This minimizes the need for additional hardware while preserving the ability to create realistic signal simulations.

Generate multi-level signals with programmable ISI and jitter up to 6  $\mbox{Gb/s}$

#### Scenarios

In aerospace and defense, technology is evolving to wider bandwidths without compromising on resolution.

The foundation is digital technology, which is becoming more prevalent because it provides advantages such as reduced size, lower power requirements, better calibration and faster volume scans.

When developing radar systems, real-life testing is very expensive. Simulations with highly realistic signals help reduce the cost of system testing. The Keysight M8190A addresses these needs with three key capabilities: wide bandwidth, high resolution and long play times.

# Real-time digital signal processing with Keysight proprietary ASIC

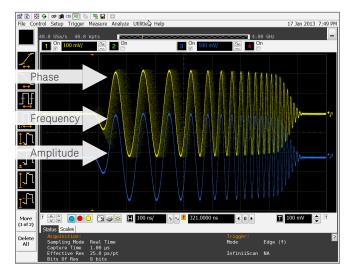

Digital up-conversion takes testing one step further. The wide bandwidth allows generating the IF signal directly. The IQ data will be upconverted digitally in hardware which gives you best signal quality in the desired frequency range. The frequency resolution is very precise with sample clock down to the picosecond range. In addition efficient memory usage allows to extend the playtime by up to 1 million times. For example for a radar signal the waveform needs to be stored only once and amplitude, frequency and phase are stored independently. Precise carrier frequency, phase and amplitude settings is possible in real-time under sequencer control. Even complex operations such as frequency sweep are possible. Streaming functionality is available for infinite playtime. Endless scenarios can be played.

Radar chirp with phase changes on the fly

Push radar and electronic warfare designs farther with highly realistic signal scenarios

## Infinite playtime

## Streaming and memory ping pong

While up to 2G Samples of waveform memory and a powerful sequencing engine provide sufficient playtime for most cases, there are some applications, such as radar scenario simulations, where playtimes in the order of several minutes are required.

In another class of applications, the number of possible waveform segments is too large to be pre-loaded into the waveform memory. An example might be NPR measurement where thousands of waveform combinations are required to cover all test cases and the signal must not be interrupted.

To address these applications, the M8190A offers the unique capability to download waveforms into portions of the waveform memory while the generator is running. In its simplest form, two waveform segments (A and B) are defined and while the generator outputs segment A repetitively, software can update segment B. Using a software command, the generator switches over to output segment B and while B is output, segment A can be overwritten and so on. This functionality is often referred to as "memory ping pong".

Taking this a step further, the waveform memory can be split up into a certain number (>= 5) of waveform segments which are linked together as a ring buffer (i.e.  $A \rightarrow B \rightarrow C \rightarrow D \rightarrow E \rightarrow A \rightarrow B$ , etc.). The generator sequentially outputs each waveform segment and as soon as it proceeds to the next one, the software loads a new waveform into this segment. This mode of operation is referred to as streaming.

Trigger

Trigger

Trigger

Pulse 3

Pulse 4

Pulse 5

Pulse 6

Pulse 7

Pulse 7

Pulse 8

Already played

In continuous streaming mode, the generator proceeds from one segment to the next without any pauses. Obviously, this mode requires the software and controlling PC to deliver new waveform segments fast enough to keep up with the rate that the waveforms are output.

In triggered streaming mode, the generator proceeds to the next segment upon an internal or external trigger event. This mode is particularly useful for pulsed radar simulations, where short pulses are interleaved with long pauses with a certain on/off ratio. Depending on the on/off ratio, the required throughput for waveform download can be dramatically reduced (resp. the output bandwidth during pulse on-time increased).

Streaming works best in conjunction with Digital Up-conversion Mode, because the baseband information can be provided at a much lower sample rate – independent of the carrier frequency.

## Infinite playtime (continued)

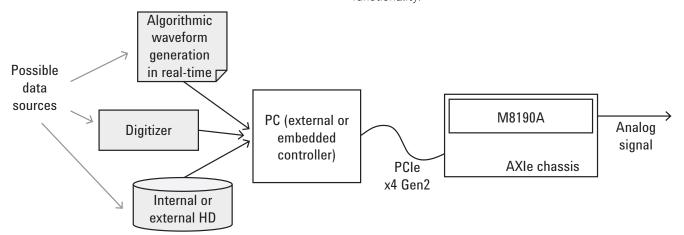

#### Data sources

Waveform data for streaming can be retrieved from a number of sources:

- Harddisk typically a fast RAID drive or Solid State Drive (SSD), which offers sufficient data throughput for continuous streaming.

- Algorithmically generated typically a pre-calculated set of waveforms that are available in PC memory. User software can select which waveform is used at which point in time.

- From Digitizer to realize capture/replay scenarios.

## Thoughput and achievable bandwidth

For continuous streaming, the hardware and software on the controlling PC must be able to deliver data fast enough to keep up with waveform generation. On a high-end PC, a thoughput of 500 – 600 MByte/s are achievable. In Digital Up-conversion mode, this corresponds to a modulation bandwidth of 125 – 150 MHz (4 bytes per I/Q sample pair). In triggered streaming mode, approx. 2 GHz modulation bandwidth can be achieved. This is the maximum that can be achieved in DUC mode – depending on the on/off ratio of the signal (please refer to publication no. 5991–3937EN).

#### Availability

The memory ping-pong and streaming functionality is available starting with M8190A firmware Rev. 3.0. An example program in C++ (both source and executable) is provided with the firmware installation that realizes the streaming functionality.

#### Headroom

Accurate emulation of transmissions—from ground station to airborne transceiver to distant ground station—includes interference, fading and more.

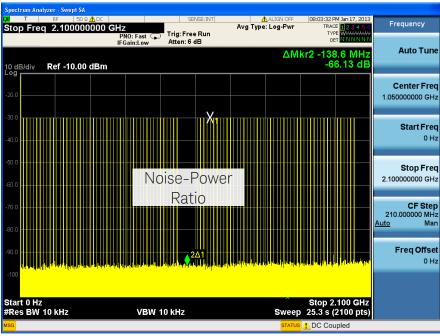

High numbered digital modulations transport more data in the same bandwidth, but tend to produce inaccurate levels and phase angles. Detailed testing becomes very important.

As a result, it is necessary to create high-quality signals with 14-bit resolution SFDR less than -90 dBc. This excellent SFDR ensures that tones stand out from distortion, even with hundreds of tones. The 2 GSa memory ensures that you can

store more than one signal scenario and simply switch between segments via direct memory access and the dynamic sequence control input.

The M8190A gives you the versatility to define new signals—proprietary, next-generation and beyond. The 5 GHz modulation bandwidth gives you enough headroom to test and address next-generation modulation schemes.

Multi-tone signal – 100 tone from 0 to 2.1 GHz (Fs = 7.2 GHz, sin(x)/x compensated)

Build a strong foundation for highly reliable satellite communications

#### **Product Structure**

The AWG has a modular product structure and requires an AXIe chassis (please see page 13)

| M8190A                                                  | Option | Software<br>upgradeable | Comment                                                                                   |

|---------------------------------------------------------|--------|-------------------------|-------------------------------------------------------------------------------------------|

| 1 channel                                               | 001    |                         | MUST order either 001 or 002                                                              |

| 2 channel                                               | 002    |                         | or LPN (requires customer-provided external                                               |

| 2 channels with Low Phase Noise                         | LPN    |                         | clock source)                                                                             |

| 14 bit/8 GSa/s <sup>1</sup>                             | 14B    | Χ                       | MUST order either 1/P or 12C or both entions                                              |

| 12 GSa/s/12 bit <sup>1</sup>                            | 12G    | Χ                       | MUST order either 14B or 12G or both options                                              |

| Additional DC and AC amplifier <sup>1</sup>             | AMP    | Χ                       |                                                                                           |

| Digital up-conversion to carrier frequency <sup>1</sup> | DUC    | Χ                       |                                                                                           |

| Upgrade from 128 MSa to 2 GSa<br>memory per channel     | 02G    | Χ                       | 2 channel version requires Option 02G (quantity 2)                                        |

| Sequencer <sup>1</sup>                                  | SEQ    | Χ                       |                                                                                           |

| Fast switching <sup>1</sup>                             | FSW    | X                       | Fast switching for 12 GSa/s requires export control license FSW is included in 14B option |

| ISO 17025                                               | 1A7    |                         | Calibration actions                                                                       |

| Z540                                                    | Z54    |                         | Calibration options                                                                       |

<sup>1.</sup> Only quantity 1 is required for 2 channel version

Bundles including AXIe chassis are available under:

M8190A -BU1 5 slot chassis, with embedded PC 16 GB RAM and Windows Embedded Standard 7 operating system: 64 bit M8190A -BU2 2 slot chassis (connectivity accessories will be added automatically - choice between desktop and laptop cabling) M8190S Multichannel Arbitrary Waveform Generator System (4- & 8 channels are selectable)

#### Acccessories

| M8190A-801 | Microwave phase matched balun, 6.5 GHz, max SMA jack                        |

|------------|-----------------------------------------------------------------------------|

| M8190A-805 | Low pass filter, 2800 MHz, max SMA, VLF 2850+                               |

| M8190A-806 | Low pass filter, 3900 MHZ max SMA, VLF 3800+                                |

| M8190A-810 | Cable assembly coaxial–50 $\Omega$ , SMA to SMA, 457 mm length              |

| M8190A-811 | Cable assembly coaxial–50 $\Omega$ , SMA to SMA, 1220 mm length             |

| M8190A-815 | Dynamic control input cable                                                 |

| M8190A-820 | Connector-RF, SMA termination, plug straight, 50 $\Omega$ , 12.4 GHz, 0.5 W |

## The Instrument

# Challenge the Boundaries of Test Keysight Modular Products

Two slot AXIe chassis with M8190A AWG

Five slot AXle chassis with two M8190A AWG; can contain an embedded controller

#### **AXIe**

The M8190A is a modular instrument packaged in the AXIe form factor. AXIe is a new open standard for high-performance, modular instrumentation, and incorporates the best features of other modular formats including VXIbus, LXI and PXI. Keysight offers a line of scalable chassis in this powerful format. Along with controller options, these AXIe chassis can form the basis of high-performance, AXIe-based test systems.

Two form factors are available: two-slot and five-slot chassis. These include an embedded AXIe system module that does not occupy a module slot. In addition, an AXIe controller is an entire system that can control the AWG. This controller consumes one module slot in the chassis.

The chassis can be used on the bench or in a rack, occupying only 4U of rack space. Keysight computer I/O cards are also available for AXIe systems.

- M9502A-U20: 2-slot AXIe chassis with USB option

- M9505A-U20: 5-slot AXIe chassis with USB option

- M9045B: PCIe laptop card adapter Gen 1 x4

- M9048A: PCle desktop card adapter Gen 2 x8

- Y1200B: x4 x8 PCIe cable

- Y1202A: x8 x8 PCIe cable

- M9536A: Embedded AXIe controller

- M8192A Multi-Channel Synchronization Module for M8190A AWG

# Performance Specification

| General characteristics                                                    |                                        |                                          |

|----------------------------------------------------------------------------|----------------------------------------|------------------------------------------|

| Digital to analog converter                                                |                                        |                                          |

| Option: –14B                                                               | Resolution<br>Sample rate              | 14 bit<br>125 MSa/s to 8 GSa/s           |

| Option: –12G                                                               | Resolution<br>Sample rate              | 12 bit<br>125 MSa/s to 12 GSa/s          |

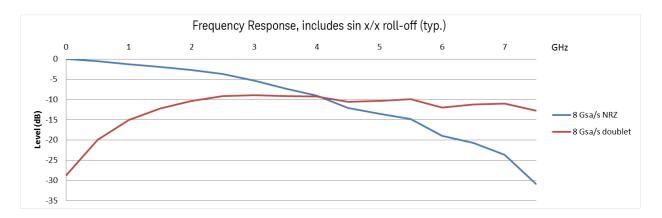

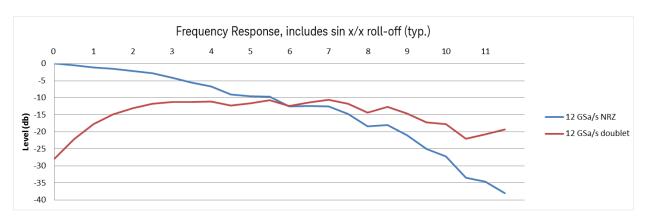

| Sin (x)/x roll-off (mathematically calculated)                             |                                        |                                          |

| Option: –14B                                                               | Sin (x)/x (-1 dB)<br>Sin (x)/x (-3 dB) | 2.1 GHz @ 8 GSa/s<br>3.5 GHz @ 8 GSa/s   |

| Option: –12G                                                               | Sin (x)/x (-1 dB)<br>Sin (x)/x (-3 dB) | 3.1 GHz @ 12 GSa/s<br>5.3 GHz @ 12 GSa/s |

| Frequency switching characteristics                                        |                                        |                                          |

| Effective output frequency ( $f_{max}$ is determined as $f_{Sa,max}/2.5$ ) |                                        |                                          |

| Option: –14B                                                               | $f_{max} = 3.2 \text{ GHz}$            |                                          |

| Option: –12G                                                               | $f_{max} = 4.8 \text{ GHz}$            |                                          |

| Effective frequency switching time <sup>1</sup>                            |                                        |                                          |

| Option: –14B <sup>2</sup>                                                  | 313 ps (= 1/ f <sub>max</sub> )        |                                          |

| Option: –12G                                                               | No option:                             | –FSW 105 μs to 210 μs                    |

| Option: –12G                                                               | Option:                                | -FSW 208 ps (= $1/f_{max}$ )             |

|                                                                            |                                        |                                          |

Determines the minimum time needed to switch between selected segments in sequence mode.

Option FSW does not affect switching time in 14 bit mode (Option 14B).

| Direct out1/direct out2                              |                                                                     |

|------------------------------------------------------|---------------------------------------------------------------------|

| Type of output                                       | Single-ended <sup>1</sup> or differential, DC-coupled               |

| Skew between normal and complement outputs           | 0 ps (nom)                                                          |

| Skew accuracy between normal and complement outputs  | ± 5 ps (typ)                                                        |

| Impedance                                            | 50 Ω (nom)                                                          |

| Amplitude control                                    | Specified into 50 $\Omega$                                          |

| Range, single-ended (DNRZ/NRZ Mode) <sup>6</sup>     | $350~\mathrm{mV}_\mathrm{p-p}$ to $700~\mathrm{mV}_\mathrm{p-p}$    |

| Resolution                                           | $30\mu V$ (nom)                                                     |

| DC accuracy, offset = 0 V (DNRZ/NRZ Mode) $^{\rm 6}$ | ± (1.5% + 15 mV) (spec)                                             |

| Offset                                               | –20 mV to + 20 mV, single-ended into 50 $\Omega$                    |

| Offset resolution                                    | 60 μV (nom)                                                         |

| DC offset accuracy                                   | ± 10 mV (spec)                                                      |

|                                                      | Common mode offset and differential offset is seperately adjustable |

| Connector type                                       | SMA                                                                 |

<sup>1.</sup> Unused output must be terminated with 50  $\Omega$  to GND. 6. Doublet mode does not allow DC signal generation.

| NRZ/DNRZ mode                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|--------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bandwidth (3 dB) <sup>2</sup>                                      | 3.0 GHz (typ)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Bandwidth (5 dB)                                                   | 5.0 GHz (typ)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Harmonic distortion 7.2 GSa/s <sup>3,5</sup>                       | $-72~\mathrm{dBc~(typ,}~f_\mathrm{out} = 100~\mathrm{MHz}) \\ -68~\mathrm{dBc~(typ)},~f_\mathrm{out} = 10~\mathrm{MHz}~~500~\mathrm{MHz},~\mathrm{measured~DC~to~3~GHz} \\ -60~\mathrm{dBc~(typ)}~,~f_\mathrm{out} = 500~\mathrm{MHz}~~3000~\mathrm{MHz},~\mathrm{measured~DC~to~3~GHz}$                                                                                                                                                                                                                                                                                                                                                                                                  |

| Harmonic distortion 12 GSa/s <sup>4, 5</sup>                       | $-54$ dBc (typ) $f_{out}$ = 100 MHz<br>-50 dBc (typ) $f_{out}$ = 10 MHz 5000 MHz, measured DC to 5 GHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| SFDR in 14 bit mode <sup>3,5</sup> (excluding harmonic distortion) | In Band Performance:  -90 dBc (typ), fout = 100 MHz, measured DC to 2 GHz -80 dBc (typ), fout = 10 MHz500 MHz, measured DC to 500 MHz -76 dBc (typ), fout = 500 MHz1 GHz, measured DC to 1 GHz -68 dBc (typ), fout = 1 GHz2 GHz, measured DC to 2 GHz -62 dBc (typ), fout = 2 GHz3 GHz, measured DC to 3 GHz  Adjacent Band Performance: -80 dBc (typ), fout = 10 MHz500 MHz, measured DC to 1.5 GHz -73 dBc (typ), fout = 500 MHz1 GHz, measured DC to 3 GHz -68 dBc (typ), fout = 1 GHz2 GHz, measured DC to 3 GHz -62 dBc (typ), fout = 2 GHz3 GHz, measured DC to 3 GHz                                                                                                               |

| SFDR in 12 bit mode <sup>4,5</sup> (excluding harmonic distortion) | In Band Performance:  -90 dBc (typ), fout = 100 MHz, measured DC to 2 GHz -80 dBc (typ), fout = 10 MHz500 MHz, measured DC to 500 MHz -78 dBc (typ), fout = 500 MHz1 GHz, measured DC to 1 GHz -73 dBc (typ), fout = 1 GHz2 GHz, measured DC to 2 GHz -68 dBc (typ), fout = 2 GHz3 GHz, measured DC to 3 GHz -60 dBc (typ), fout = 3 GHz5 GHz, measured DC to 5 GHz  Adjacent Band Performance: -80 dBc (typ), fout = 10 MHz500 MHz, measured DC to 1.5 GHz -73 dBc (typ), fout = 500 MHz1 GHz, measured DC to 3 GHz -68 dBc (typ), fout = 1 GHz2 GHz, measured DC to 5 GHz -64 dBc (typ), fout = 2 GHz3 GHz, measured DC to 5 GHz -60 dBc (typ), fout = 3 GHz5 GHz, measured DC to 5 GHz |

| Two-tone IMD <sup>3</sup>                                          | TTIMD = -73 dBc (typ), $f_{out1} = 499.5$ MHz, $f_{out2} = 500.5$ MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

<sup>2.</sup> t, bandwidth: BW = 0.25/t, 3. SCLK = 7.2 GSa/s, amplitude = 700 mV<sub>p-p</sub>, double NRZ mode, excluding  $f_{sa}$  - 2 \*  $f_{out}$ , fSa - 3 \*  $f_{out}$ . 4. SCLK = 12 GSa/s, amplitude = 700 mVp-p, double NRZ mode, excluding  $f_{sa}$  - 2 \*  $f_{out}$ , fSa - 3 \*  $f_{out}$ . 5. Measured with a balun such as the 5310A from Pico Second Pulse Labs plus 10 dB attenuator.

<sup>6.</sup> Doublet mode does not allow DC signal generation.

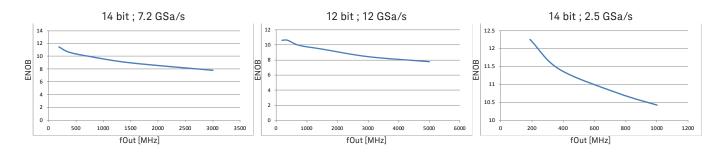

#### **ENOB** vs. frequency

| Doublet mode                                                                      |                                                                                                                                    |

|-----------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|

| Bandwidth                                                                         | See frequency plot (measured) 8 GHz/12 GHz, single ended                                                                           |

| Harmonics 14 bit doublet mode 1 8 GSa/s                                           | $\rm f_{out} = 5400~MHz \ldots 6500~MHz$ measured 5.4 GHz to 6.5 GHz, no harmonics in this range                                   |

| Harmonics 12 bit doublet mode <sup>2</sup> 12 GSa/s                               | $\rm f_{out}$ = 8100 MHz 9900 MHz, measured 8.1 GHz to 9.9 GHz, no harmonics in this range                                         |

| SFDR in 14 bit doublet mode <sup>1</sup> 8 GSa/s (excluding harmonic distortion)  | $-48~\text{dBc}$ (typ) $f_{\text{out}} = 5400~\text{MHz} \dots 6500~\text{MHz},$ measured 5.4 GHz to 6.5 GHz, Single ended         |

| SFDR in 12 bit doublet mode <sup>2</sup> 12 GSa/s (excluding harmonic distortion) | $-44~\mathrm{dBc}$ (typ) $\mathrm{f_{out}} = 8100~\mathrm{MHz} \dots 9900~\mathrm{MHz},$ measured 8.1 GHz to 9.9 GHz, Single ended |

<sup>1.</sup> SCLK = 8 GSa/s, amplitude = 700 mV  $_{\rm p,p}$ , double NRZ mode, excluding f  $_{\rm Sa}$  – 2 \* f  $_{\rm out}$ , f  $_{\rm Sa}$  – 3 \* f  $_{\rm out}$ . 2. SCLK = 12 GSa/s, amplitude = 700 mV  $_{\rm p,p}$ .

Two selectable output paths per channel are available when Option AMP is installed: 1) DC output path 2) AC output path.

| Amp out1/amp out2                                   |                                                                                                           |

|-----------------------------------------------------|-----------------------------------------------------------------------------------------------------------|

| DC output                                           |                                                                                                           |

| Output type                                         | Single-ended <sup>1</sup> or differential, DC-coupled                                                     |

| Impedance                                           | 50 Ω (nom)                                                                                                |

| Amplitude                                           | 500 mV $_{pp}$ to 1.0 V $_{pp}$ , single-ended into 50 $\Omega$ (overprogramming down to 150 mV possible) |

| Amplitude resolution                                | 300 μV (nom)                                                                                              |

| DC amplitude accuracy                               | $\pm$ (2.5% + 10 mV) (nom) <sup>2</sup>                                                                   |

| Voltage window                                      | $-1.0$ V to + 3.3 V $^{3},$ single-ended into 50 $\Omega$                                                 |

| Offset resolution                                   | 600 µV (nom)                                                                                              |

| DC offset accuracy                                  | $\pm$ 2.5% $\pm$ 10 mV (typ) $\pm$ 4% of amplitude (typ) $^{4}$                                           |

| Termination voltage window                          | $-1.5$ V to + $3.5$ V $^3$                                                                                |

| Termination voltage resolution                      | 300 μV (nom)                                                                                              |

| Skew between normal and complement outputs          | 0 ps (nom)                                                                                                |

| Skew accuracy between normal and complement outputs | ± 5 ps (typ)                                                                                              |

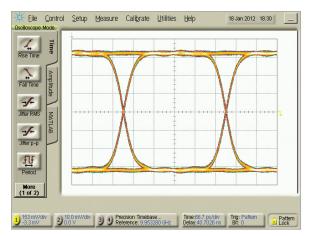

| Rise/fall time (20% to 80%)                         | $<$ 60 ps (typ) $^{5}$                                                                                    |

| Jitter (peak-peak)                                  | 15 ps (typ) <sup>5</sup>                                                                                  |

| Overshoot                                           | $5\%$ (typ) $^6$                                                                                          |

| Connector type                                      | SMA                                                                                                       |

- Unused output must be terminated with 50 Ω to the termination voltage.

Termination voltage = 0 V; adjusted at 23 °C ambient temperature, amplitude reduces by 2 mV/°C (typ) for ambient temperature above 23 °C, amplitude increases by 5 mV/°C (typ) for ambient temperature below 23 °C³.

- Termination voltage window: offset ± 1V.

- Termination voltage = 0 V.

- 5. PRBS  $2^{11}$  1,  $f_{Sa}$  = 12 GSa/s, data rate = 3 Gb/s, triggered on sample clock out, NRZ mode.

Eye pattern with amplitude 1000 mV with 0 V offset

| AC output                                   |                                                                                                                   |

|---------------------------------------------|-------------------------------------------------------------------------------------------------------------------|

| Output type                                 | Single-ended, AC coupled Front-panel marking: amp out1 for channel 1; amp out2 for channel 2                      |

| Impedance                                   | 50 Ω (nom)                                                                                                        |

| Amplitude                                   | 200 mV $_{pp}$ to 2.0 V $_{pp}^{-1}$ , single-ended into 50 $\Omega$                                              |

| Amplitude resolution                        | 0.25 dB (nom)                                                                                                     |

| Amplitude accuracy                          | $\pm$ 0.5 dB $^{1}$ (typ)                                                                                         |

| Bandwidth (3 dB)                            | 50 MHz to 5 GHz (typ)                                                                                             |

| Harmonic distortion <sup>2</sup>            | $<$ $-39$ dBc (typ), $f_{out} = 375$ MHz, measured DC to 3 GHz                                                    |

|                                             | $<\!-37$ dBc (typ), $\rm f_{out}^{} = 100$ MHz 3000 MHz, measured 100 MHz to 3 GHz                                |

| Harmonic distortion <sup>3</sup>            | $<$ $-39$ dBc (typ) $f_{out} = 375$ MHz, measured DC to 5 GHz                                                     |

|                                             | $<$ $-37$ dBc (typ) f $_{\rm out}$ = 100 MHz 5000 MHz, measured DC to 5 GHz                                       |

| SFDR in 14 bit mode <sup>2</sup> (excluding | harmonic distortion) <sup>5</sup>                                                                                 |

|                                             | $<\!-60$ dBc (typ), $\rm f_{out}^{}=100~MHz$ 2000 MHz, measured 100 MHz to 3000 MHz                               |

|                                             | $<\!-56$ dBc (typ), $\rm f_{out}^{}\!=2000$ MHz 3000 MHz, measured 100 MHz to 3000 MHz                            |

| SFDR in 12 bit mode <sup>3</sup> (excluding | harmonic distortion)                                                                                              |

|                                             | $<\!-60$ dBc (typ), $\rm f_{out}^{}=100~MHz$ 2000 MHz, measured 100 MHz to 5000 MHz                               |

|                                             | $<\!-56$ dBc (typ), $\rm f_{out}^{}\!=2000$ MHz 3000 MHz, measured 100 MHz to 5000 MHz                            |

|                                             | $<\!-50$ dBc (typ), $\rm f_{out}^{}\!=3000~MHz$ 5000 MHz, measured 100 MHz to 5000 MHz                            |

| Amplitude flatness <sup>4</sup>             | 100 MHz to 1 GHz (typ), + 1.5 dB to $-0.5$ dB 100 MHz to 4 GHz (typ) +/- 0.1 dB with calibration / pre-distortion |

|                                             | 1 GHz to 4 GHz (typ), -2 dB to + 3 dB                                                                             |

| Two-tone IMD <sup>2</sup>                   | TTIMD = $-46 \text{ dBc (typ)}$ , $f_{\text{out1}} = 999.5 \text{ MHz}$ , $f_{\text{out2}} = 1000.5 \text{ MHz}$  |

| Connector type                              | SMA                                                                                                               |

|                                             |                                                                                                                   |

<sup>1. 500</sup> MHz sine wave.

SOLK = 7.2 GSa/s, amplitude = 1 V<sub>p-p</sub>, 14 bit mode, double NRZ mode, excluding f<sub>Sa</sub> - 2\*f<sub>out</sub>, f<sub>Sa</sub> - 3\*f<sub>out</sub>.

SCLK = 12 GSa/s, amplitude = 1 V<sub>p-p</sub>, 12 bit mode, double NRZ mode, excluding f<sub>Sa</sub> - 2\*f<sub>out</sub>, f<sub>Sa</sub> - 3\*f<sub>out</sub>.

SCLK = 12 GSa/s, amplitude = 1 V<sub>p-p</sub>, normalized to 100 MHz; 12 bit mode, includes sin (x)/x compensation.

SFDR numbers for interpolation mode are the same as the SFDR numbers for 14 bit mode. For further specification please see the digital up-conversion specification.

| Marker outputs                        |                                                                                                          |

|---------------------------------------|----------------------------------------------------------------------------------------------------------|

| Number of markers                     | Two markers per channel:<br>Sample marker<br>Sync marker                                                 |

| Output type                           | Sample marker: single-ended<br>Sync marker: single ended                                                 |

| Sync marker out1/sync marker out2     |                                                                                                          |

| Output impedance                      | 50 Ω (nom)                                                                                               |

| Timing resolution <sup>1</sup>        | N sample clock cycles $(N = 64 \text{ in } 12 \text{ bit mode}; N = 48 \text{ in } 14 \text{ bit mode})$ |

| Level                                 |                                                                                                          |

| Voltage window                        | −0.5 V to 2.0 V                                                                                          |

| Amplitude                             | 200 mV $_{\rm pp}$ to 2.0 V $_{\rm pp}$                                                                  |

| Resolution                            | 10 mV                                                                                                    |

| Accuracy                              | $\pm (10\% + 25 \text{ mV}) \text{ (typ)}$                                                               |

| Rise/fall time (20% to 80%)           | 150 ps (nom)                                                                                             |

| Width <sup>1</sup>                    | User-defined in multiples of N sample clock cycles ( $N=64$ in 12 bit mode; $N=48$ in 14 bit mode)       |

| Connector type                        | SMA                                                                                                      |

| Sample marker out1/sample marker out2 |                                                                                                          |

| Timing resolution <sup>1</sup>        | 1 sample clock cycle                                                                                     |

| Level                                 |                                                                                                          |

| Voltage window                        | −0.5 V to 2.0 V                                                                                          |

| Amplitude                             | 200 mV $_{\rm pp}$ to 2.0 V $_{\rm pp}$                                                                  |

| Resolution                            | 10 mV                                                                                                    |

| Accuracy                              | ± (10% + 25 mV) (typ)                                                                                    |

| Rise/fall time<br>(20% to 80%)        | 150 ps (nom)                                                                                             |

| Width                                 | 49 sample clocks in 12 bit mode<br>40 sample clocks in 14 bit mode                                       |

| Random jitter                         | 5 ps RMS (typ)                                                                                           |

| Connector type                        | SMA                                                                                                      |

<sup>1.</sup> See characteristics digital up-conversion if interpolation is enabled.

A common trigger/gate input for both channels is provided on the front panel. This input is used to start a sequence or a scenario.

| Threshold                                                           | 5 V to +5 V<br>5 V to +5 V                             |

|---------------------------------------------------------------------|--------------------------------------------------------|

|                                                                     | 5 V to +5 V                                            |

| Range -                                                             | 5 V to +5 V                                            |

|                                                                     |                                                        |

| Resolution 10                                                       | 00 mV                                                  |

| Sensitivity 2                                                       | 00 mV                                                  |

| Polarity                                                            | electable positive or negative                         |

| Drive S                                                             | electable channel 1, channel 2 or both                 |

| Input Impedance 1                                                   | $k\Omega$ or 50 $\Omega$ (nom), DC coupled             |

| Max toggle frequency                                                |                                                        |

| 12 bit mode S.                                                      | ample clock output frequency divided by 320            |

| 14 bit mode S                                                       | ample clock output frequency divided by 240            |

| Minimum pulse width                                                 |                                                        |

| Asynchronous timing between trigger/gate and 1. sync clock output   | .1 * sync clock period                                 |

| Synchronous timing between trigger/gate input and Sync clock output | ee set-up and hold timing under timing characteristics |

| Connector type S                                                    | MA                                                     |

A common dynamic control input for both channels is provided on the front panel. The user can select, if the dynamic control input affects none, only channel 1/channel 2 only, or both channels. A detailed description of the dynamic control input including timing diagram and pin assignment is shown in the M8190A User's Guide.

| Dynamic control input                       |                                                                                          |

|---------------------------------------------|------------------------------------------------------------------------------------------|

| Input signals                               | Data[012]_In + Data_Select + Load <sup>1</sup>                                           |

| Internal data width                         | 19 bit, multiplexed using Data_Select                                                    |

| Data_Select                                 | Data_Select = Low: Data[012] = Data[012]_In Data_Select = High: Data[1318] = Data[05]_In |

| Number of addressable segments or sequences | $2^{19} = 524\ 288$                                                                      |

| Data rate                                   | DC to 1 MHz                                                                              |

| Set-up time                                 | 3.0 ns ('Data[012]_In, 'Data_Select' to rising edge of 'Load')                           |

| Hold time                                   | 0.0 ns (rising edge of `Load' to `Data[012]_In, `Data_Select')                           |

| Minimum <sup>3</sup> latency <sup>4</sup>   | Dynamic control input to direct out                                                      |

| 12 bit mode                                 | 27520 sample clock cycles (meas)                                                         |

| 14 bit mode                                 | 20640 sample clock cycles (meas)                                                         |

| Interpolation mode <sup>5</sup>             |                                                                                          |

| Input range                                 |                                                                                          |

| Low level                                   | 0 V to +0.7 V                                                                            |

| High level                                  | +1.6 V to +3.6 V                                                                         |

| Impedance                                   | Internal 1 $k\Omega$ pull-down resistor to GND                                           |

| Connector                                   | 20 pin mini D ribbon (MDR) connector <sup>2</sup> , cable Option 815                     |

Data[0...12]'\_In and `Data\_Select' will be stored on rising edge of `Load signal.'

Manufacturer Part Number: N10220-52B2PC. Manufacturer: 3M.

<sup>3.</sup> As the current segment (or sequence or scenario) is always completed, the total latency is determined by the duration of the segment (or sequence or scenario). See characteristics of digital up-conversion if interpolation is enabled.

<sup>4.</sup> See characteristics digital up-conversion if interpolation is enabled.

The M8190A can operate synchronously or asynchronously. Synchronous operation must be selected to achieve minimum delay uncertainty between Trigger Input, Event, Input or Dynamic Control Input and Direct Out or Marker Out. For synchronous operation Trigger/Gate Input, Event, Input or Dynamic Control must be synchronous to the Sync Clock Output.

| Timing characteristics                           |                                                                                                                                            |

|--------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| Setup time                                       |                                                                                                                                            |

| Trigger/gate in to rising edge of sync clock out | 10.5 ns (typ)                                                                                                                              |

| Event in to rising edge of sync clock out        | 10.5 ns (typ)                                                                                                                              |

| Hold time                                        |                                                                                                                                            |

| Rising edge of sync clock out to trigger/gate in | -7.5 ns (typ)                                                                                                                              |

| Rising edge of sync clock out to event in        | -7.5 ns (typ)                                                                                                                              |

| Delay in 12 bit mode                             |                                                                                                                                            |

| Trigger/event in to direct/DC/AC out             | 10240 external sample clock cycles + 0.5 internal <sup>1</sup> sample clock cycles (nom)                                                   |

| Sync marker to direct/DC/AC out                  | 0.5 internal sample clock cycles - 4.9 ns (nom) (fSa $\geq$ 6.4 GSa/s) 0.5 internal sample clock cycles - 8.0 ns (nom) (fSa $<$ 6.4 GSa/s) |

| Delay in 14 bit mode                             |                                                                                                                                            |

| Trigger/event in to direct/DC/AC out             | 7680 external sample clock cycles + 0.5 internal <sup>1</sup> sample clock cycles (nom)                                                    |

| Sync marker to direct/DC/AC out                  | 0.5 internal sample clock cycles - 4.9 ns (nom) (fSa $>= 4.8$ GSa/s) 0.5 internal sample clock cycles - 8.0 ns (nom) (fSa $< 4.8$ GSa/s)   |

| Sample marker to direct/DC/AC out                | 0.5 internal <sup>1</sup> sample clock cycles - 1.3 ns (nom)                                                                               |

<sup>1.</sup> Internal sample clock cycles. For definition of 'Internal sample clock cycles' refer to sample clock outputs specification.

| Delay uncertainty |                                          |

|-------------------|------------------------------------------|

| Asynchronous mode |                                          |

|                   | 64 external sample clocks in 12 bit mode |

|                   | 48 external sample clocks in 14 bit mode |

| Synchronous mode  | 10 ps (typ) <sup>2</sup>                 |

<sup>2.</sup> The delay accuracy in synchronous mode is equal to the peak-peak jitter between sync clock output and direct out.

Note: Timing characteristics of DUC, see digital up-conversion (DuC) chapter

#### Variable delay

In order to compensate for e.g. external cable length differences as well as the initial skew, channel 1 and channel 2 can be independently delayed with a very high timing resolution.

Setting the variable delay of channel 1 to 10 ps has following effect:

Direct out1 (or amp out1, if selected) and sample marker out1 are delayed by 10 ps with respect to following signals: sample clock out, sync marker out1, sync marker out2, direct out2 (or amp out2, if selected), trigger/gate input, event input

Note: Modifying the variable delay of one channel always affects the delay of the analog output AND the sample marker of that channel.

The variable delay is split into two delay elements:

- 1. Fine delay

- 2. Coarse delay

The variable delay is the sum of fine delay and coarse delay. If a de-skew between channel 1 and channel 2 is needed, adjust in the first step the coarse delay to the optimum position. In the second step, use the fine delay to perfectly align both channels.

| Variable delay                                         |                           |

|--------------------------------------------------------|---------------------------|

| Variable delay                                         | Fine delay + coarse delay |

| Variable delay range                                   |                           |

| $f_{Sa} \ge 6.25 \text{ GSa/s}$                        | 0 ps to 10.030 ns         |

| $2.5 \text{ GSa/s} \le f_{Sa} < 6.25 \text{ GSa/s}$    | 0 ps to 10.060 ns         |

| f <sub>sa</sub> < 2.5 GSa/s                            | 0 ps to 10.150 ns         |

| Fine delay                                             |                           |

| The fine delay is independently adjustable for channel | el 1 and channel 2        |

| Delay range                                            |                           |

| $f_{Sa} \ge 6.25 \text{ GSa/s}$                        | 0 ps to 30 ps             |

| $2.5 \text{ GSa/s} \le f_{Sa} < 6.25 \text{ GSa/s}$    | 0 ps to 60 ps             |

| f <sub>sa</sub> < 2.5 GSa/s                            | 0 ps to 150 ps            |

| Delay resolution                                       | 50 fs                     |

| Accuracy                                               |                           |

| $f_{Sa} \ge 6.25 \text{ GSa/s}$                        | ± 10 ps (typ)             |

| $2.5 \text{ GSa/s} \le f_{Sa} < 6.25 \text{ GSa/s}$    | ± 20 ps (typ)             |

| f <sub>sa</sub> < 2.5 GSa/s                            | ± 20 ps (typ)             |

|                                                        |                           |

<sup>1.</sup> For definition of "internal sample clock cycles", refer to sample clock output specification. Note for delay in interpolation mode: Please see digital up-conversion specification.

| Coarse delay                                        |                         |

|-----------------------------------------------------|-------------------------|

| The coarse delay is independently adjustable for ch | annel 1 and channel 2   |

| Delay range                                         | 0 ps to 10 ns, variable |

| Delay resolution                                    |                         |

| f <sub>sa</sub> ≥ 6.25 GSa/s                        | 10 ps                   |

| 2.5 GSa/s ≤ f <sub>Sa</sub> < 6.25 GSa/s            | 20 ps                   |

| f <sub>sa</sub> < 2.5 GSa/s                         | 50 ps                   |

| Accuracy                                            |                         |

| $f_{Sa} \ge 6.25 \text{ GSa/s}$                     | ± 20 ps (typ)           |

| $2.5 \text{ GSa/s} \le f_{Sa} < 6.25 \text{ GSa/s}$ | ± 20 ps (typ)           |

| f <sub>sa</sub> < 2.5 GSa/s                         | ± 50 ps (typ)           |

When the variable delay is set to 0 ps, the channels operate in coupled mode and the same amplifier path for both channels is selected, the initial skew between channel 1 and channel 2 is 0 ps.

| Initial skew between channel 1 and channel 2 |               |

|----------------------------------------------|---------------|

| Skew <sup>1</sup>                            | 0 ps (nom)    |

| Accuracy                                     | ± 20 ps (typ) |

<sup>1.</sup> Coupling on, same amplifier path is selected for channel 1 and channel 2.

| Reference clock output |                                                                                                                                |

|------------------------|--------------------------------------------------------------------------------------------------------------------------------|

| Source                 | Internal backplane 100 MHz                                                                                                     |

| Frequency              | 100 MHz                                                                                                                        |

| Stability              | ± 20 ppm (typ.) (see M9502A/M9595A Data Sheet)                                                                                 |

| Aging                  | ± 1 ppm per year                                                                                                               |

| Source                 | Internal Oven-Controlled Reference Oscillator                                                                                  |

| Frequency              | 100 MHz                                                                                                                        |

| Accuracy               | ± 0.2 ppm (typ.)                                                                                                               |

| Stability              | ± 0.6 ppm (typ.)                                                                                                               |

| Aging                  | ± 0.3 ppm per year (typ.)                                                                                                      |

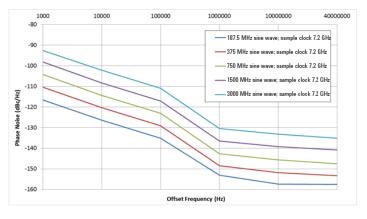

| Phase Noise            | -95 dBc/Hz @ 10 Hz, -125 dBc/Hz @ 100 Hz offset (typ.) Phase noise at offsets > 100 Hz (refer to phase noise plots on page 30) |

| Source                 | External REF CLK In                                                                                                            |

| Frequency              | 100 MHz                                                                                                                        |

| Amplitude              | 1 $V_{pp}$ into 50 $\Omega$ (nom)                                                                                              |

| Source impedance       | $50\Omega$ , AC coupled (nom)                                                                                                  |

| Connector              | SMA                                                                                                                            |

| Reference clock input  |                                                                                                                                |

| Input frequencies      | Selectable 1 MHz to 200 MHz, in steps of 1 MHz                                                                                 |

| Lock range             | ± 35 ppm (typ)                                                                                                                 |

| Frequency resolution   | 1 MHz                                                                                                                          |

| Input level            | 100 mV $_{pp}$ to 2 V $_{pp}$                                                                                                  |

| Impedance              | $50\Omega$ , AC coupled (nom)                                                                                                  |

| Connector type         | SMA                                                                                                                            |

| Sync clock output      |                                                                                                                                |

| Frequency              |                                                                                                                                |

| 14 bit mode            | Sample clock divided by 48 (sample clock source is always channel 1)                                                           |

| 12 bit mode            | Sample clock divided by 64 (sample clock source is always channel 1)                                                           |

| Interpolation mode     | Sample clock divided by (24 x interpolation factor)                                                                            |

| Output amplitude       | 1.0 $V_{pp}$ (nom) into 50 $\Omega$                                                                                            |

| Impedance              | 50 Ω nominal, AC coupled                                                                                                       |

SMA

Connector

#### Sample clock

There are two selectable sources for the sample clock:

- Internal synthesizer

- Sample clock input

The two channel instrument (Option 002) offers the flexibility to independently select the sample clock sources for channel one and channel two. If different clock sources are selected for the channels, both channels operate entirely independently with respect to sample rate and sequencing.

| Internal synthesizer clock characteristics |                                                                                                                                                                                                                                                                                                                                                                      |

|--------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Frequency                                  | 125 MHz to 12 GHz                                                                                                                                                                                                                                                                                                                                                    |

| Accuracy                                   | ± 20 ppm                                                                                                                                                                                                                                                                                                                                                             |

| Frequency resolution                       | 15 digits, e.g. 10 μHz at 1 GHz                                                                                                                                                                                                                                                                                                                                      |

| Phase noise <sup>1</sup>                   | $\begin{split} f_{Sa} &= 1 \text{ GHz} < -110 \text{ dBc/Hz (typ) at } 10 \text{ kHz offset, } f_{out} = 125 \text{ MHz}^2 \\ f_{Sa} &= 8 \text{ GHz} < -105 \text{ dBc/Hz (typ) at } 10 \text{ kHz offset, } f_{out} = 1.0 \text{ GHz}^2 \\ f_{Sa} &= 12 \text{ GHz} < -105 \text{ dBc/Hz (typ) at } 10 \text{ kHz offset, } f_{out} = 1.5 \text{ GHz} \end{split}$ |

| Sample clock input           |                             |

|------------------------------|-----------------------------|

| Frequency range <sup>1</sup> | 1 GHz to 12 GHz             |

| Input power range            | +0 dBm to +7 dBm            |

| Damage level                 | +8 dBm                      |

| Input impedance              | 50 $\Omega$ nom, AC coupled |

| Connector type               | SMA                         |

<sup>1.</sup> The sample clock output is derived from the internal sample clock  $f_{Sa,i}$ . For  $f_{Sa,i}$  = 500 MSa/s...1 GSa/s the sample clock output is twice of  $f_{Sa,i}$ . For  $f_{Sa,i}$  = 250 MSa/s ... 500 MSa/s the sample clock output is four times  $f_{Sa,i}$ . For  $f_{Sa,i}$  = 125 MSa/s ... 250 MSa/s the sample clock output is eight times  $f_{Sa,i}$ .

eight times f<sub>Sa,i</sub>.

2. Measured at "data out".

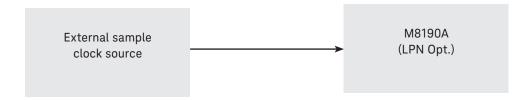

| Low Phase Noise clock input (only with option | on LPN)                    |

|-----------------------------------------------|----------------------------|

| Frequency range                               | 1 GHz to 12 GHz            |

| Input power range                             | +0 dBm to + 7 dBm          |

| Damage level                                  | +10 dBm                    |

| Input impedance                               | $50\Omega$ nom, AC coupled |

| Transition time                               | < 1 ns                     |

| Connector type                                | SMA                        |

Configuring the instrument for low phase noise mode forces the channels to operate in coupled and reduced noise floor mode. In this case the fine delay feature is disabled.

The frequency of the external low phase noise clock must be set in the External Sample Frequency box on the clock panel. All other features of the instrument function the same as for standard operation.

#### Phase noise

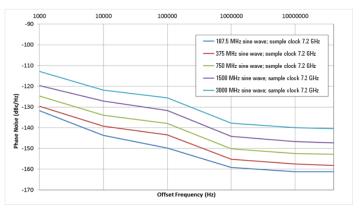

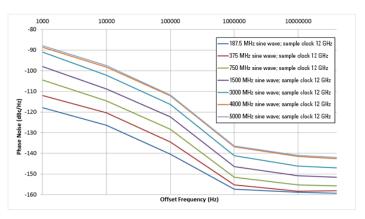

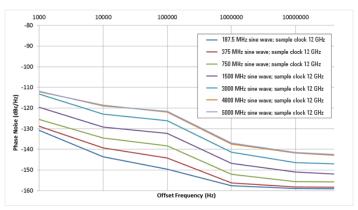

These plots show the typical phase noise using the delay adjustment

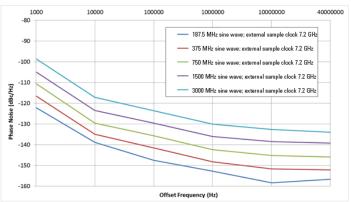

Phase noise plot with internal sample clock, 7.2 GSa/s, direct output measured with balun

Phase noise plot with external sample clock, 7.2 GSa/s, direct output measured with balun

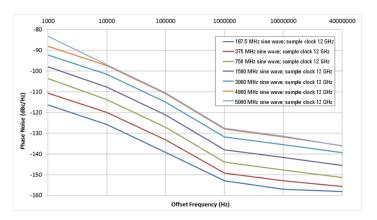

Phase noise plot with internal sample clock, 12 GSa/s, direct output measured with balun

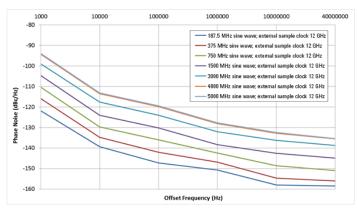

Phase noise plot with external sample clock, 12 GSa/s, direct output measured with balun

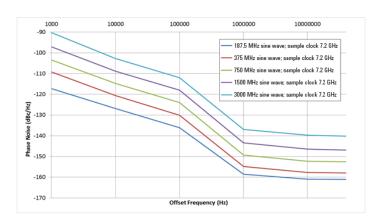

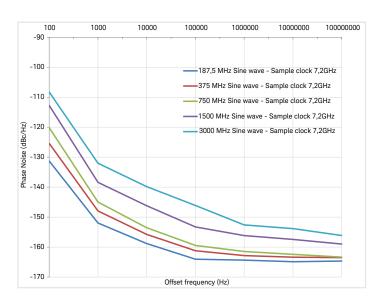

#### These plots show the typical phase noise without using the delay adjustment

Phase noise with internal sample clock 7.2 GSa/s, direct out measured with balun and reduced noise floor

Phase noise with external sample clock 7.2 GSa/s, direct out measured with balun and reduced noise floor

Phase noise with internal sample clock 12 GSa/s, direct out measured with balun and reduced noise floor

Phase noise with external sample clock 12 GSa/s, direct out measured with balun and reduced noise floor

#### Phase noise

This plot show the typical phase noise with the low phase noise option (opt. LPN)

Option LPN significantly improves the arbitrary waveform generator phase noise performance. With option LPN a customer-supplied external synthesizer (1–12 GHz range) must be connected. The measurements in the following graph were performed using a Keysight proprietary external oscillator and measured using a Keysight E5052B signal source analyzer.

The source for the sample clock output can be either the internal synthesizer or the sample clock input. The source for the sample clock output can be independently selected from the sample clock. For example, it is possible to operate the sample clock output from the internal synthesizer at  $f_1$  to clock the DUT; as an example,  $f_1$  may be divided by two by the DUT. In this case,  $f_1/2$  can be connected to the sample clock input as to be used as the sample clock of the M8190A.

| Sample clock output          |                                                        |

|------------------------------|--------------------------------------------------------|

| Source                       | Selectable, internal synthesizer or sample clock input |

| Frequency range <sup>1</sup> | 1 GHz to 12 GHz                                        |

| Output amplitude             | 400 mVpp (nom), fix                                    |

| Input impedance              | 50 $\Omega$ (nom), AC coupled                          |

| Transition time (20% to 80%) | 20 ps (typ)                                            |

| Connector                    | SMA                                                    |

The following table shows which sample clock out routings are possible if coupling is on.

|           | Coupling = on         |        | Channel 1      |                |                |                |

|-----------|-----------------------|--------|----------------|----------------|----------------|----------------|

|           |                       |        | External clock |                | Internal clock |                |

|           |                       | 12 bit | 14 bit         | 12 bit         | 14 bit         |                |

|           | External clock        | 12 bit | External clock | _              | _              | _              |

| Channel 2 | External Clock        | 14 bit | _              | External clock | _              | _              |

|           | latered deal.         | 12 bit | _              | _              | Internal clock | _              |

|           | Internal clock 14 bit |        | _              | -              | _              | Internal clock |

The following table shows which sample clock out routings are possible if coupling is off.

|                   |                     |                | Channel 1                       |                                 |                                 |                                 |

|-------------------|---------------------|----------------|---------------------------------|---------------------------------|---------------------------------|---------------------------------|

| Coupling = off    |                     | External clock |                                 | Internal clock                  |                                 |                                 |

|                   |                     | 12 bit         | 14 bit                          | 12 bit                          | 14 bit                          |                                 |

| Channel 2  Channe | Channel 2 operate   | 12 bit         | External or inter-<br>nal clock |

|                   | clock               | 14 bit         | External or inter-<br>nal clock |

|                   | Channel 2 operate   | 12 bit         | External or inter-<br>nal clock | External or inter-<br>nal clock | External or inter-<br>nal clock | _                               |

|                   | with internal clock | 14 bit         | External or inter-<br>nal clock | External or inter-<br>nal clock | _                               | External or inter-<br>nal clock |

<sup>1.</sup> The sample clock output is derived from the internal sample clock  $f_{Sa,i}$ . For  $f_{Sa,i}$  = 500 MSa/s...1 GSa/s the sample clock output is twice of  $f_{Sa,i}$ . For  $f_{Sa,i}$  = 250 MSa/s ... 250 MSa/s the sample clock output is eight times  $f_{Sa,i}$ .

#### Coupling between channel 1 and channel 2

The two channel instrument (Option 002) has two distinct modes of operation: coupling = off and coupling = on.

#### Coupling = off

- The two channels operate entirely independently

- The channels may run at different sample clock rates

- The channels may run from the same clock source (internal or external)

- The channels may operate from different clock sources (internal or external)

- The channels are being started asynchronously

- Following parameters can be changed individually per channel:

- Frequency

- Amplitude, offset

- Amplifier path

- Waveform

- Sequence

- Trigger mode (auto, triggered, gated)

- Start/stop (programming/programming complete)

- 12 bit or 14 bit mode (see limitations in table below)

- Dynamic sequencing on/off

- Following parameters can only be changed for both channels:

- None

The following table shows which mode combinations are available, if coupling is off.

|                |                       |                | Channel 1 |                |           |           |

|----------------|-----------------------|----------------|-----------|----------------|-----------|-----------|

| Coupling = off |                       | External clock |           | Internal clock |           |           |

|                |                       | 12 bit         | 14 bit    | 12 bit         | 14 bit    |           |

| Channel 2      | Futornal alask        | 12 bit         | Available | Available      | Available | Available |

|                | External clock        | 14 bit         | Available | Available      | Available | Available |